### zeligsoft THALES

Experience Report: Rapid Model-Driven Waveform Development with UML

**Presented by: Shaw-Ping Lee**

SDR'08 Technical Conference – 26-30 October 2008 Proceeding of the SDR 08 Technical Conference and Product Exposition. Copyright @ 2008 SDR Forum. All Rights Reserved

- Introduction

- Waveform Development

- Results

- Future Improvements

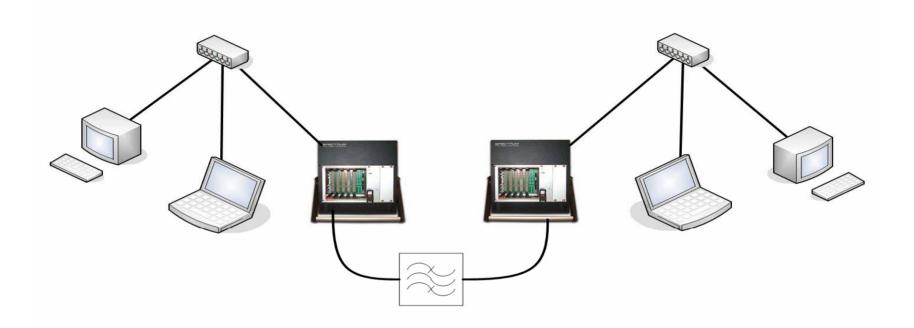

- SDR-4000 point-to-point video demonstration (~ 30 seconds)

- An R & D project design and develop SCA WNW waveform for Software Defined Radio.

- Target hardware is not available at the beginning early development on host PC.

- Solution must consider portability (to target) and reusability.

- Not aware of existing solution at the time.

- Need a well defined development process for future projects use.

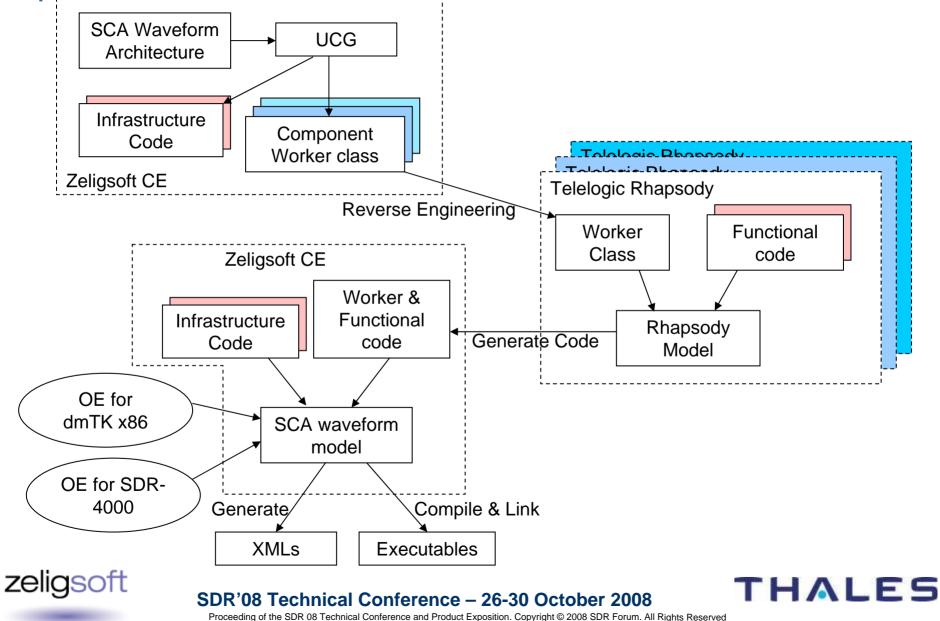

- Define architecture of the waveform in Zeligsoft CE.

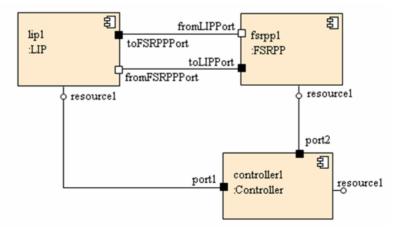

- Components have Uses and Provides ports.

- Component definition translates to OE independent worker code and infrastructure code.

#### SDR'08 Technical Conference – 26-30 October 2008

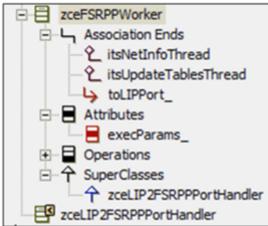

- Worker source code is reversed-engineered into a class in Rhapsody.

- Uses ports shows up as private association.

- Provides Ports shows up as virtual function to be implemented.

- Some infrastructure behaviors terminate in the

| zceFSRPPW orker                                                                       |          |

|---------------------------------------------------------------------------------------|----------|

| 😑 exec Params_;FSR PP_p arams                                                         | <b>-</b> |

|                                                                                       |          |

| 20 20 EF SRPPW ork er (exe oP arams :0 on st                                          |          |

| ₩ ~zoeFSR PPWorke ()<br>initExe cParams(params:const FSRPP                            |          |

| config_ShortTime out(shorttime out con                                                |          |

| config_EnableMPR (enablempr: const C                                                  |          |

| query_ShortTimeout(shorttimeout:CO                                                    |          |

| ☐ query_En ab leMPR (e na blempr: CORBA: ☐ CF_LifeCy cle_initialize(portIdentifier:in |          |

| CF_LifeCycle_releaseObject(portIdent                                                  |          |

| CF_Resource_start( port Identifier in t):                                             |          |

| CF_Resource_stop(portidentifier.int); v                                               |          |

| UP2FSR PP_OnewayPus h(portident if i                                                  |          |

| UP2FSR PP_Sy no Pus K portI de nt ifier:i                                             |          |

| ■settoLIPPort(toLIPPortzoeFSR PP2LIP                                                  |          |

|                                                                                       |          |

worker.

#### SDR'08 Technical Conference – 26-30 October 2008

- Rhapsody model generate source code.

- Makefiles are different for each target.

- Waveform is built incrementally. Many iterations of modifications.

- Modifications need to propagate from waveform model to Rhapsody model.

- Only modifications to interfaces, properties, and ports on a component need to propagate.

- Manually vs. reverse-engineer.

- Infrastructure code and functional code.

- 2 ORBs ACE TAO and ORBexpress.

- ORB functions are encapsulated in infrastructure code.

- Makefiles cleverly make the switch between ORB.

- 2 execution environments.

- QualNet multi-hop test-bed to emulate PHY and verify host PC implementation.

- Next, waveform is ported to target.

- Less than 3 weeks of porting.

zeliasott

Technical Conference – 26-30 October 2008 Proceeding of the SDR 08 Technical Conference and Product Exposition. Copyright © 2008 SDR Forum. All Rights Reserved

- Time Saving Porting time is reduced.

- No requirement for in-house CORBA and SCA experts – shorter learning curve.

- Extra abstraction codes to make clean separation between infrastructure and functional code – but the overhead is small.

- UML improves code quality and code readability.

- Look into the possibility to extend the process to DSP and FPGA in future project.

- Automated integration between Zeligsoft and Rhaspody.

SDR'08 Technical Conference – 26-30 October 2008

# Thank you!

## **Questions?**

Proceeding of the SDR 08 Technical Conference and Product Exposition. Copyright © 2008 SDR Forum. All Rights Reserved