### A 65nm CMOS RF Front End dedicated to Software Radio in Mobile Terminals

F. Rivet, Y. Deval, D. Dallet, JB Bégueret, D. Belot

IMS Laboratory, Université de Bordeaux, Talence, France STMicroelectronics, Crolles, France

Proceeding of the SDR 08 Technical Conference and Product Exposition. Copyright © 2008 SDR Forum. All Rights Reserved Washington D.C. – October 28th 2008

# OUTLINE

Software Radio in Mobile Terminals

## A Sampled Analog Signal Processor

- Principle and System

- Analog Discrete Electronics

- Modeling Results

- Perspectives

# OUTLINE

### Software Radio in Mobile Terminals

## A Sampled Analog Signal Processor

- Principle and System

- Analog Discrete Electronics

- Modeling Results

- Perspectives

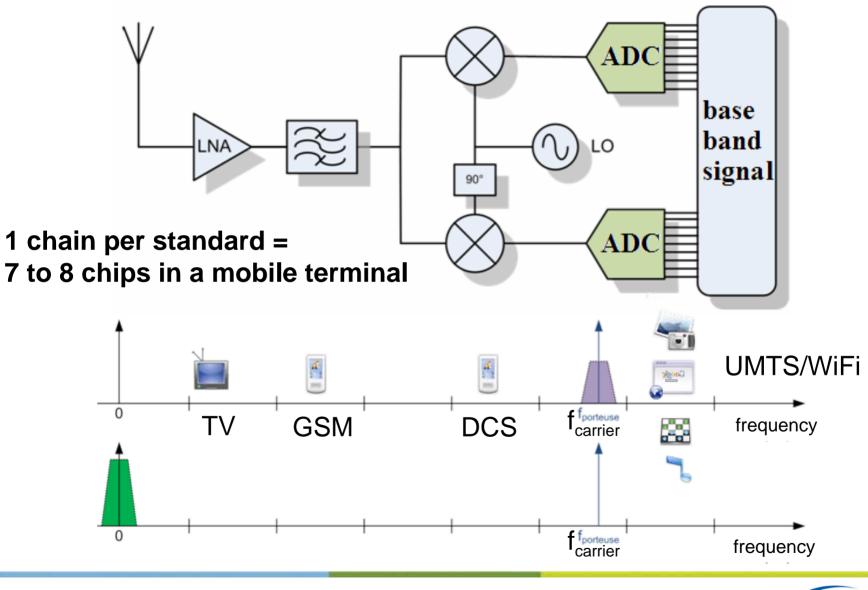

### **Classical receiving chain**

Proceeding of the SDR 08 Technical Conference and Product Exposition. Copyright © 2008 SDR Forum. All Rights Reserved Washington D.C. – October 28th 2008

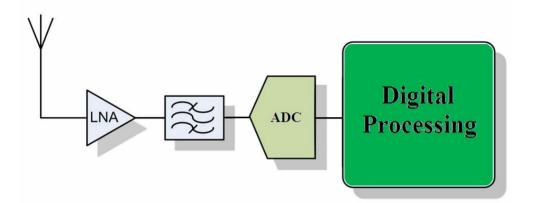

### Software Radio receiving chain

### SR receiving chain

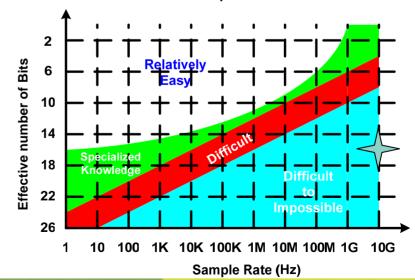

A/D conversion imposes a high power consumption at RF frequencies and high resolution

A total SR receiving chain dedicated to mobile terminals is expected to be feasible in 15 years

But ...

Some constraints

# OUTLINE

**Software Radio in Mobile Terminals**

### A Sampled Analog Signal Processor

- Principle and System

- Analog Discrete Electronics

- Modeling Results

- Perspectives

### How to make it feasible ...

- 2 Ideas are envisaged:

- An **ANALOG** circuit to work directly at RF Frequencies (10GHz at least)

- Switch from time-domain to FREQUENCY-domain signal processing

- 2 ways to challenge these ideas

- An Analog Processor working with VOLTAGE SAMPLES

- A time to frequency domain conversion ALGORITHM

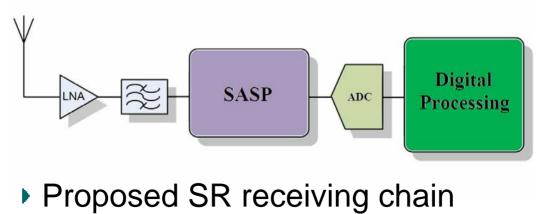

- A Sampled Analog Signal Processor (SASP) is chosen to interface antenna and A/D conversion

Proceeding of the SDR 08 Technical Conference and Product Exposition. Copyright © 2008 SDR Forum. All Rights Reserved Washington D.C. – October 28th 2008

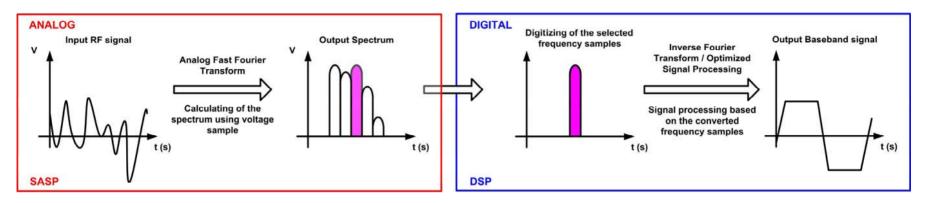

### **Software Radio Architecture**

### A principle: The Frequency Translation

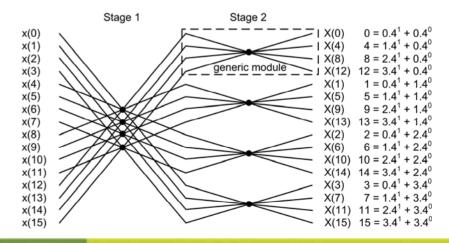

A way to do it: an Analog Fast Fourier Transform

- A pipelined FFT is chosen

- Radix-4 Butterfly algorithm

- Generic modules are to be implemented analogicaly

Proceeding of the SDR 08 Technical Conference and Product Exposition. Copyright © 2008 SDR Forum. All Rights Reserved

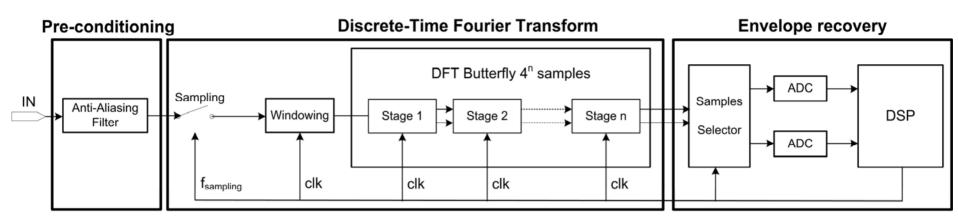

## **Software Radio Architecture**

- Analog RF signal processing:

- Anti aliasing filter

- Sampling (frequency is the parameter of reprogrammability) Avoid interferences and improve FFT calculation

- Discrete Time signal processing

- Windowing

- FFT calculation

- Spectrum output through voltage samples

- Signal envelope recover

- Samples selections

- Conversion into numerical to DSP

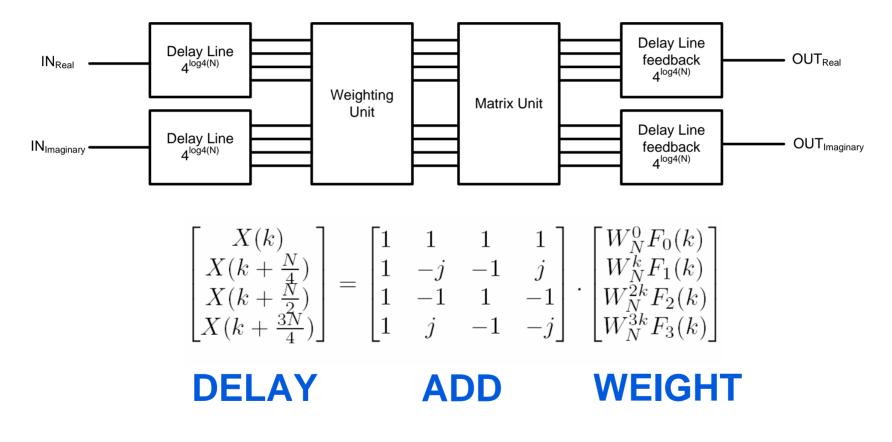

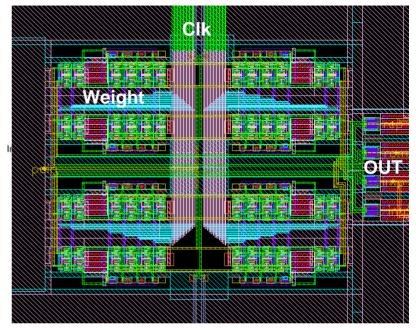

### **Discrete Analog FFT**

- Composed by generic stages based on the radix-4 butterfly algorithm

- Each stage has the same structure

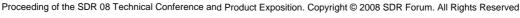

## **Discrete Analog Operations**

Delay

### **Differential structure**

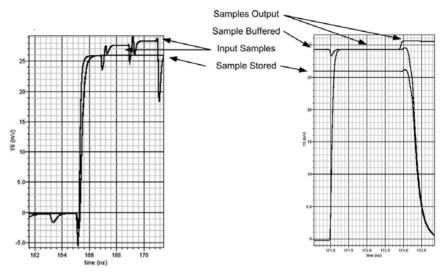

### A Charge transfer simulation

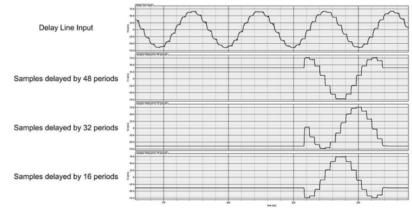

### A Delay Line simulation

Proceeding of the SDR 08 Technical Conference and Product Exposition. Copyright © 2008 SDR Forum. All Rights Reserved

BORDEAUX

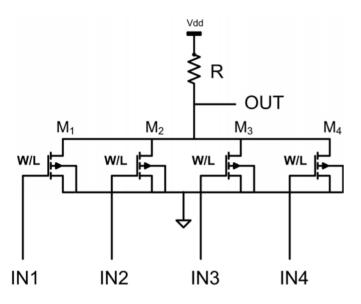

# **Discrete Analog Operations**

Adder

- Each FFT processing stage is composed by a matrix of addition and subtraction

- Adder allows to defined in hardware the add/subtract matrix

- Voltage samples are converted into current

- Current are added on one node

- The currents sum is converted into voltage

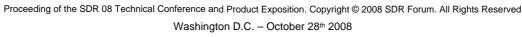

### **Discrete Analog Operations**

### Weighter

#### WEIGHTING UNIT COEFFICIENTS APPLICATION

| Switch Network Configuration |                             |                           |                           | Coefficients                                |         |                       |        |

|------------------------------|-----------------------------|---------------------------|---------------------------|---------------------------------------------|---------|-----------------------|--------|

| $S_1$                        | $S_2$                       | $S_3$                     | $S_4$                     |                                             |         |                       |        |

| Transistor Characteristics   |                             |                           |                           | For a 100mV input voltage sample simulation |         |                       |        |

| $M_1 \frac{W_1}{L} = 2.1$    | $M_2 \ \frac{W_2}{L} = 5.3$ | $M_3 \frac{W_3}{L} = 7.8$ | $M_4 \frac{W_4}{L} = 9.3$ | $cos(2\pi.nk)$                              | Output  | Effective Coefficient | Error  |

| DC                           | DC                          | DC                        | DC                        | 0                                           | 0       | 0                     | 0%     |

| DC                           | DC                          | DC                        | IN                        | 0.383                                       | 45.9mV  | 0.372                 | 2.87%  |

| DC                           | DC                          | IN                        | IN                        | 0.707                                       | 84.5mV  | 0.686                 | 2.97 % |

| DC                           | IN                          | IN                        | IN                        | 0.924                                       | 111mV   | 0.901                 | 2.48%  |

| IN                           | IN                          | IN                        | IN                        | 1                                           | 123.1mV | 1                     | 0%     |

Proceeding of the SDR 08 Technical Conference and Product Exposition. Copyright © 2008 SDR Forum. All Rights Reserved

# **A Sampled Analog Signal Processor**

Three discrete analog operations to perform the FFT

The Analog Fast Fourier Transform is performed by basic analog operations

## **A Sampled Analog Signal Processor**

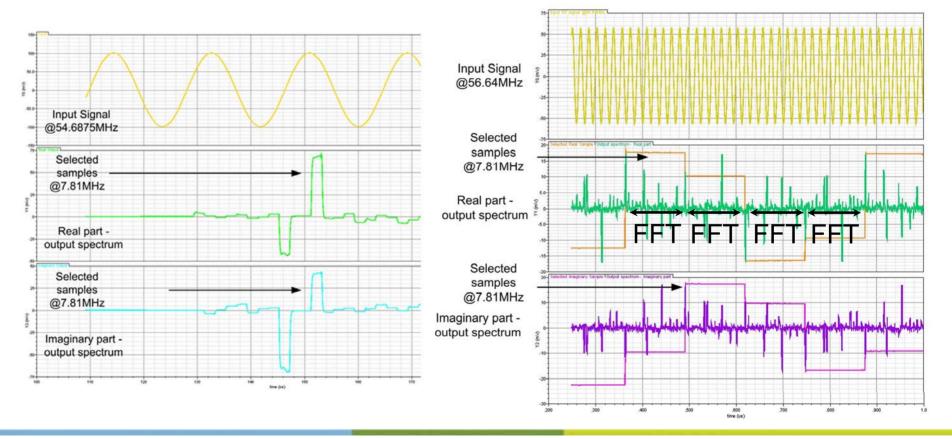

### Simulation of 64-sample SASP

$F_{sampling} = 500MHz$  $F_{in} = 7*500MHz /64$

# OUTLINE

### Software Radio in Mobile Terminals

### A Sampled Analog Signal Processor

- Principle and System

- Analog Discrete Electronics

- Modeling Results

- Perspectives

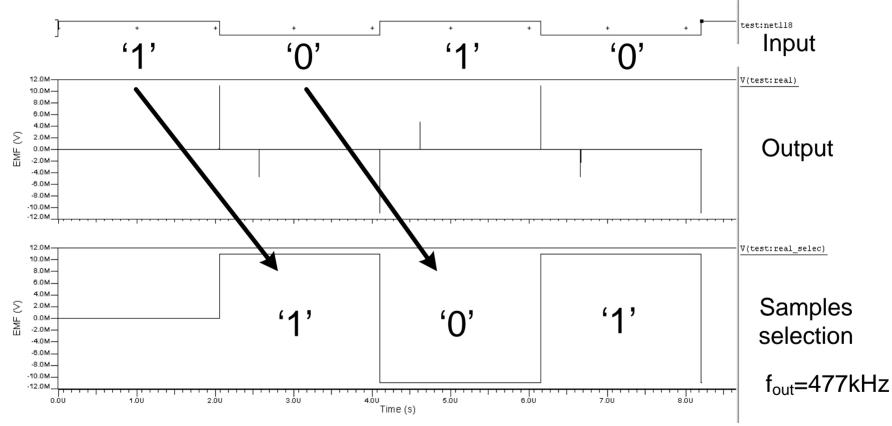

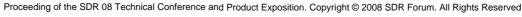

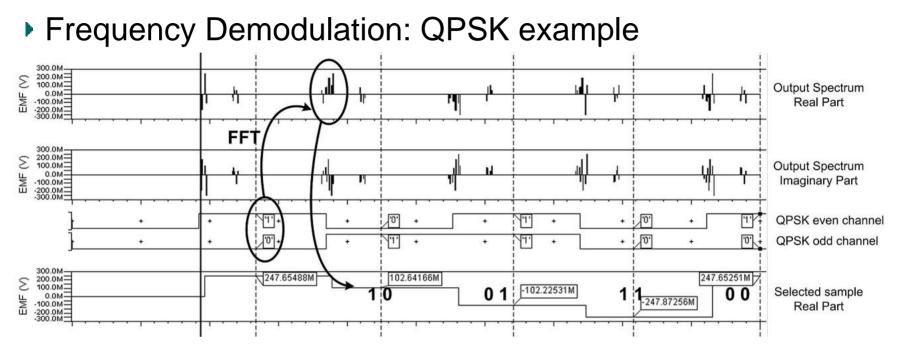

#### Frequency Demodulation: BPSK example test:net118 Input 12.0U V(test:net015) 10.0U-8.0U-6.001 **BPSK** modulation 4.011 S 2.00 Ľ. 0.00 -2.0U $f_{carrier} = 500MHz$ -4.00--6.0U--8.0U -10.0U -12.0U ™ tput SASP: 12.0M 10.0M-8.0M-6.0M-4.0M-Σ 2 0M-**Real Signal** MF 0.05 -2.0M -4.0M -6.0M -8.0M--10.0M -12.0M 12.0M V(test:imag) 10.0M-8.0M-6.0M-4.0M-EMF (V) **Imaginary Signal** 2 0M 0.0N -2.0M -4.0M--6.0M--8.0M--10.0M--12.0M 6.00 7.00 8.00 0.00 1.00 2.00 3.00 4.0U 5.00 Time (s)

Bit signatures can be directly recognized into the spectrum

Proceeding of the SDR 08 Technical Conference and Product Exposition. Copyright © 2008 SDR Forum. All Rights Reserved

Frequency Demodulation: BPSK example

► 500MHz → 477kHz : decimation by a ratio of 1000 – ADC and DSP work at low frequencies

- The four-bit signature can be identified into the spectrum

- Open window to more complex modulation types: 8-QPSK, 16-QAM, 64-QAM

# Conclusion

Optimized algorithm can be developed to demodulate signal into frequency domain – ADC requirements are totally relaxed

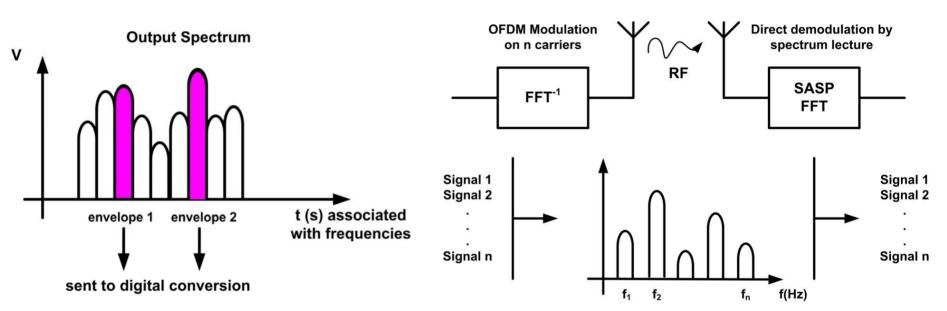

Concurrent Reception

Direct Reception

- Several signal envelops can be processed at the same time

- Military and Security applications: Listen any channel at the same time

- Commercial applications: Multiapplications devices

As a FFT is processed, the SASP displays all the sub-carriers of OFDMmodulated signals. The digital part has just to handle the sub-carriers demodulations.

## Perspectives: From a prototype to a final product

- Example of the GSM standard with a 65536-sample SASP

- ▶ T<sub>bit</sub>=3.69µs, Channel Bandwitdh=200kHz, Carrier Frequency=900MHz

- With f<sub>sampling</sub>=2.184GHz, 6 samples encoding 8 bits are displayed

- A « frequency demodulation » algorithm would support a direct demodulation from the processed spectrum

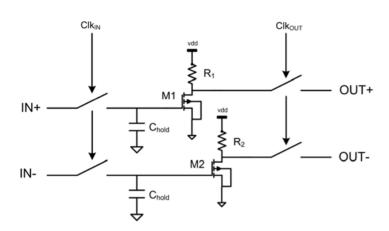

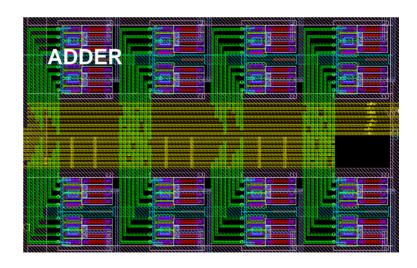

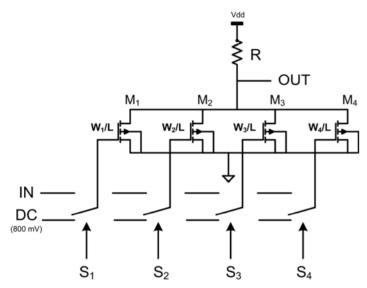

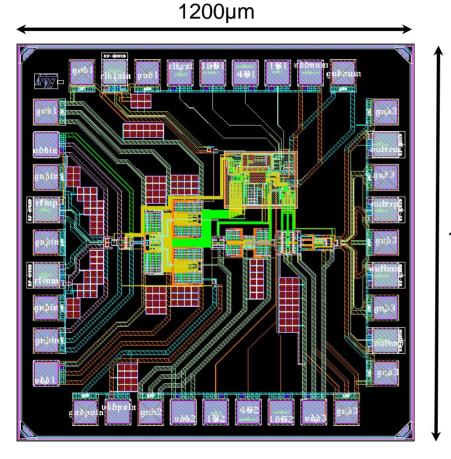

# **A Sampled Analog Signal Processor**

### Design of a 64-sample SASP

Technology: 65nm CMOS STMicrolectronics

Die Area: 1.44mm<sup>2</sup>

Maximal Frequency: 1GHz

1200µm

RF spectrum range covered: 0-500MHz

Power consumption: 360mW

▶ 64-sample SASP prototype → finalized in a 65536-sample SASP

Proceeding of the SDR 08 Technical Conference and Product Exposition. Copyright © 2008 SDR Forum. All Rights Reserved

- The SASP is an Analog Processor in Software Radio receiving chain. It is technically:

- Low Power (P<500mW)

- Low Cost (CMOS technology)

- Small Die Area (IC<5mm<sup>2</sup>)

- Relaxes ADC and DSP constraints

- The SASP re-invents RF signal processing:

- Frequency Demodulation (Optimized demodulation)

- Concurrent Reception (Resources shared)

- The SASP

- can be a solution for a true Software Radio architecture dedicated to mobile terminals

- but ... many technological challenges remain to be overcome to achieve an industrial product

### Conclusion

A 65536-sample SASP working at 10GHz is the goal to reach a complete Software Radio Processor

Proceeding of the SDR 08 Technical Conference and Product Exposition. Copyright © 2008 SDR Forum. All Rights Reserved Washington D.C. – October 28th 2008

24

## **Contact Information**

Feel free to contact me for more information

### François RIVET

- Email: francois.rivet@ims-bordeaux.fr

- Mail: IMS Lab / 351 Cours de la Libération / 33405 Talence Cedex / France

- PhD. Student IC Design Team Software Radio RFIC

### Main References

- « A Disruptive Receiver Architecture Dedicated to Software-Defined Radio », IEEE transactions on Circuits and Systems II 55, 4 (2008) 344-348

- « A Universal Radio Frequency Receiver Architecture Based on Sampled Analog Signal Processing », IEEE MWSCAS'07, Montreal, Canada

- « A Disruptive Software-Defined Radio Receiver Architecture Based on Sampled Analog Signal Processing », IEEE Radio Frequency Integrated Circuits Symposium, Honolulu, United States, June 2007