**Orchestration and Control Architecture**

# FROM LABORATORY TO THE FIELD: AN OPEN SOURCE SDR PROJECT COUPLED WITH NATIVE LINUX DRIVER FRAMEWORK

Xianjun Jiao, Wei Liu, Muhammad Aslam, Felipe A. P. F., Ingrid moerman, Filip Louagie

# **OPENWIFI** FIRST OPEN SOURCE FULL STACK REAL-TIME WI-FI

# Øpenwifi

- Motivation

- Project positioning and technical information

- License consideration and collaboration

- Development schedule

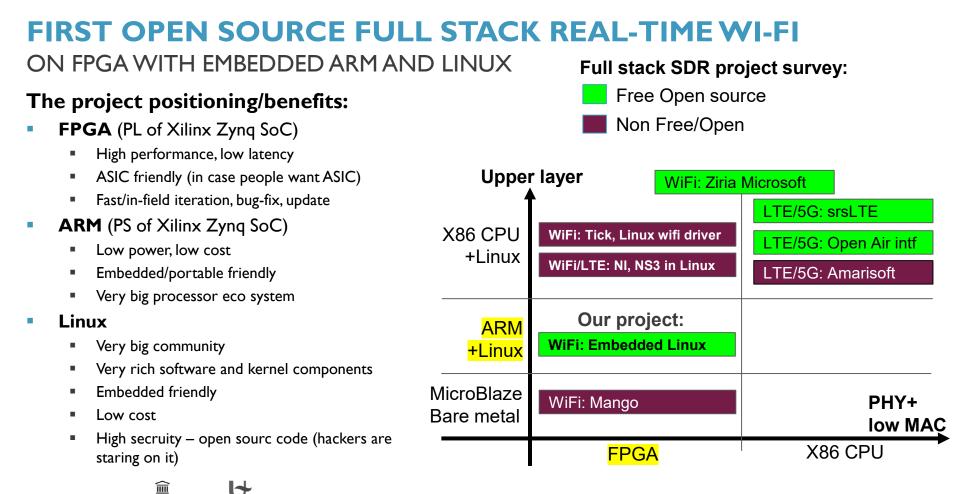

# FIRST OPEN SOURCE FULL STACK REAL-TIME WI-FI ON FPGA WITH EMBEDDED ARM AND LINUX

## MOTIVATION

You have a good idea to improve Wi-Fi:

٠

- Still no ideal SDR option for Wi-Fi research... •

- And MAC philosophy is so different: 10us SIFS (Wi-Fi) vs 4ms HARQ (LTE) Not like pure SW implementation of LTE (srsLTE, OA), Wi-Fi Op implementation needs HW acceleration, which is more challenging! Dig into commerciai cinp use special HW (not cheap) black-box. Some reverse

engineering. Good luck!

with special OS (Windows) -**Microsoft SORA/Ziria**

**Option5: DIY**....

#### **Option2:**

**Buy expensive proprietary SDR HW/SW** design with limitations. Like NI, WARP **Option4:** Use some blocks from **Gnuradio or papers. Never** get end-to-end. Most of them work in sniffing mode.

I**D**Lab

່ເກາຍດ

UNIVERSITEIT

GENT

Universiteit

Antwerpen

# IMPLEMENTATION ARCHITECTURE AND FEATURES

#### Basic features (802.11a/g; 802.11n 20MHz MCS 0~7)

- Ad-hoc mode

- AP mode

- Station mode

#### **Special features** (Survey/feedback in community/conference)

- IQ sample and spectrum sensing capability without interrupt communication

- TAISC (Flexible MAC engine) to ease MAC development

#### **Possible future features**

- Access deep PHY information: channel response, etc.

- Multi antenna support: direction finding; beamforming; MIMO

- Multiple virtual interfaces/slices from one PHY

ĪIIII

GENT

- 802.11p DSRC for V2V, most popular V2V standard

- 802.11ah

- 802.11ax

່ເກາຍດ

Community input

**ID**Lab

UNIVERSITEIT Universiteit Antwerpen

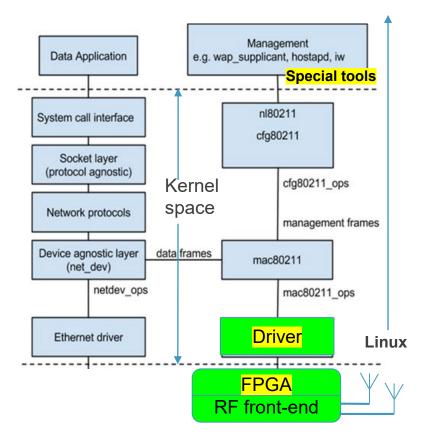

# WHAT WILL BE AVAILABLE OUT OF BOX

#### Ours: images and source code

- Precompiled images for specific hardware platform

- Linux image

- FPGA image

- Source code of software/FPGA components

- Special tools in user space to access special feature in driver and FPGA

- Linux driver

- FPGA design

#### Yours: Hardware platform

- Zedboard+ad9364 (720 euro)

- ADRV9364-Z7020 SOM + ADRVICRR-BOB carrier (750 euro)

- ADRV9361-Z7035 SOM + ADRV1CRR-BOB carrier (1300 euro)

- Zc706/zcu102+ad9361 (3250 euro)

- Xxx according to community input

# **OPEN SOURCE PLATFORM LEVERAGE FOR COLLABORATIONS** CHOICE OF OPEN SOURCE LICENSE IS IMPORTANT

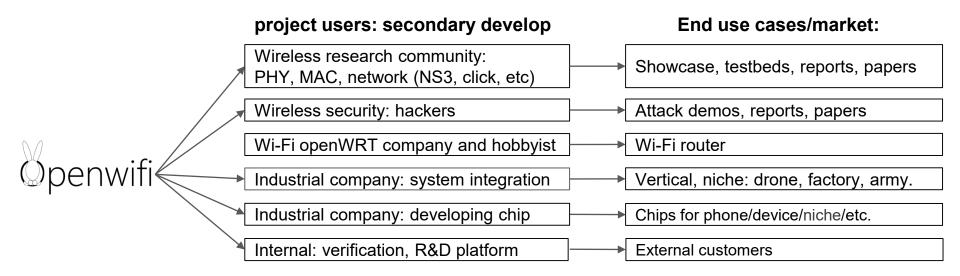

- Low-entry level for various users because of **Open Source**:

- Academic research partners and corresponding projects

- Industrial partners doing R&D

- Non-commercial usage (License type to be decided).

- For research usage without request/registration or complicated administrative procedure.

- Commercial usage, Support and Customization

- License for non-open commercial purpose

- Dedicated support service

- R&D service: adapting the implementation to customer request

Interest in the series of the

# **POTENTIAL AUDIENCES/CUSTOMERS IN OUR MIND**

### **DEVELOPMENT SCHEDULE** FIRST STABLE VERSION BY END OF THIS YEAR

Orchestration and Reconfiguration Control Architecture

# THANKS! Q&A